# arm

## CSS N2: Arm Neoverse N2 Platform, Delivered to Partners as a Fully Verified, Customizable Subsystem

Hot Chips 2023

Anitha Kona, Lead System Architect & Fellow, Arm August 28<sup>th</sup>, 2023

© 2023 Arm

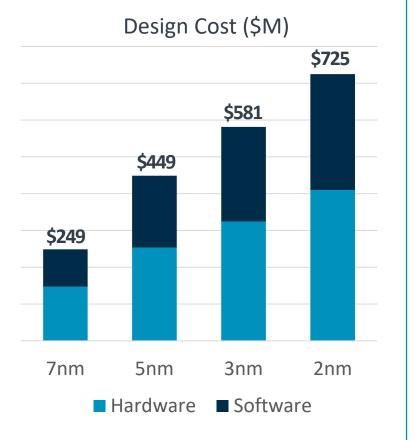

## The Pressure on Silicon Development

### **Advanced Node Cost**

Source: IBS Global Semiconductor Industry Service Report – July 2022

### Time to Market Demands

Performance MORE, MORE, MORE

Validation NO SILICON SPINS

REDUCE IT, RAMP IT

### Need for Specialized Silicon

(1) 1B 5G SUBSCRIBERS

Sustainability

Source: 2023 data. Cisco, Statistica/IDC

**arm** NEOVERSE

### DIFFERENTIATION & CUSTOMIZATION

### armneoverse

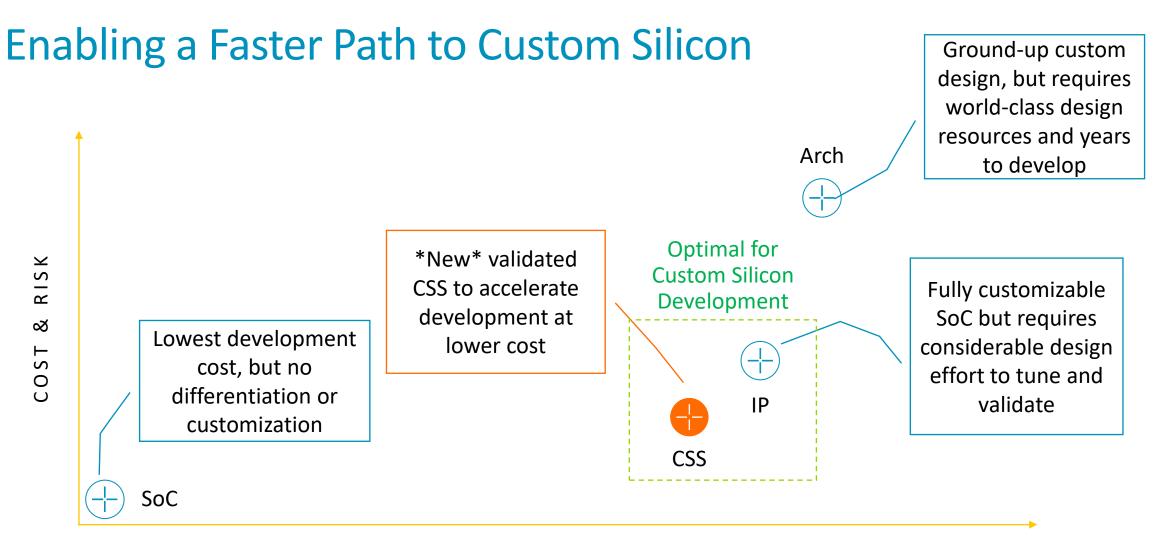

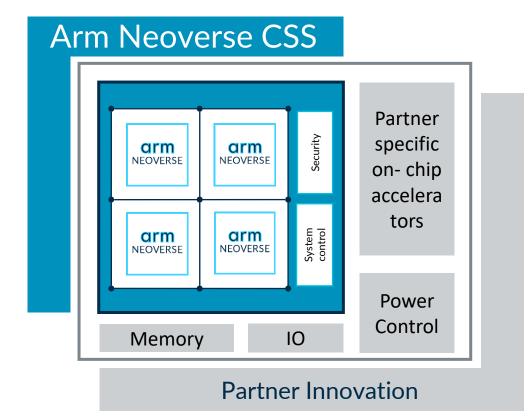

## The Relief: Arm Neoverse Compute Subsystem (CSS)

Fastest Path toProduction Silicon

+ World LeadingPerformance

Leading Edge

Technology

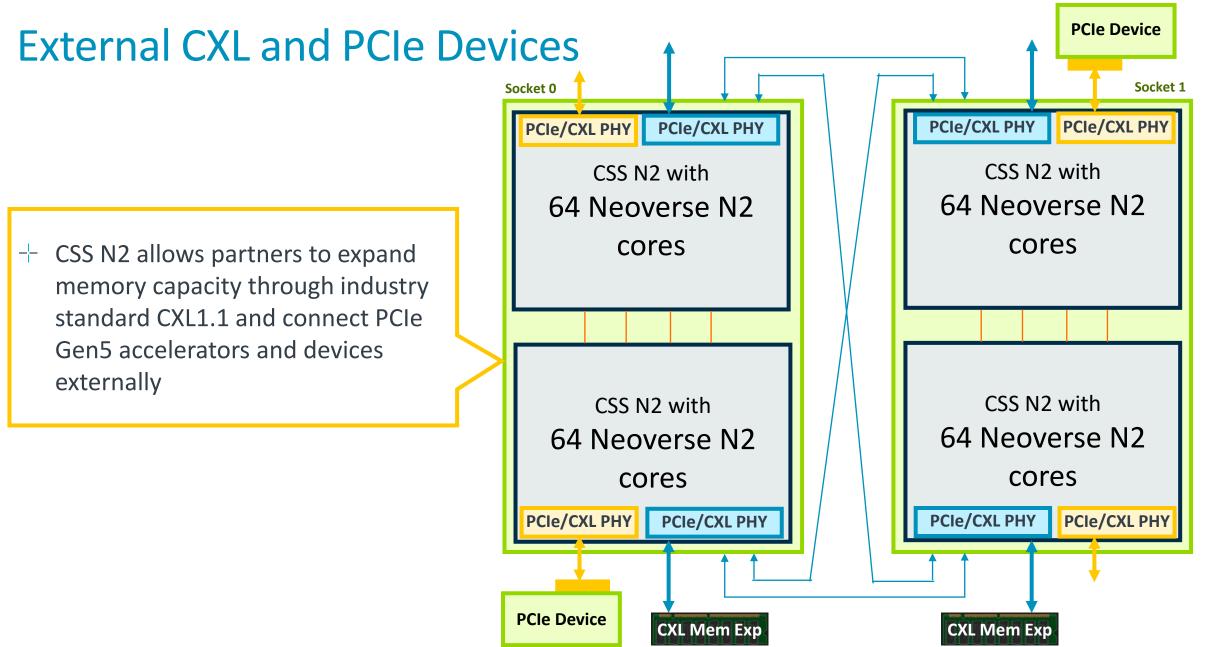

- Neoverse CSS delivers PPA optimized compute in leading edge technology node – fully validated RTL, pre-tuned implementation

- Deployment ready for emerging technologies –

PCIe Gen5, CXL-based memory-pooling

- Enables custom or heterogenous integration accelerators or specialized compute

- Can support chiplet-based designs

- SystemReady with reference SW stack

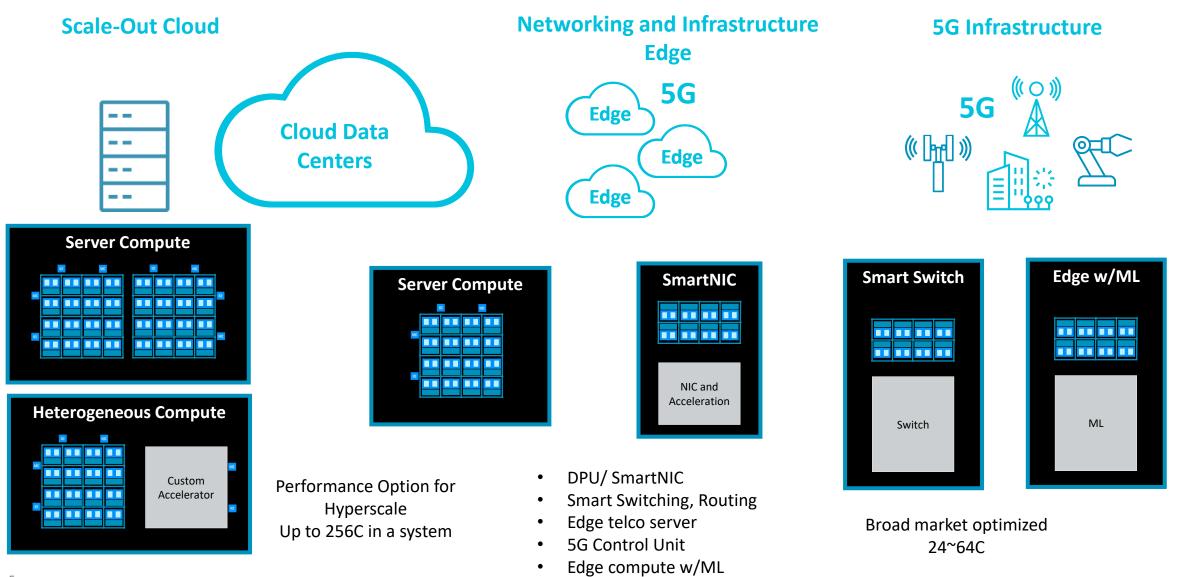

## Arm Neoverse CSS N2 Cloud-to-Edge Differentiated Solutions

### armneoverse

### Arm Neoverse CSS N2 ("CSS Genesis")

| Feature                    | 5nm Specification                                                                   |  |  |  |  |  |

|----------------------------|-------------------------------------------------------------------------------------|--|--|--|--|--|

| # of CPU Cores             | 24/32/64 N2 CPUs, 2.1-3.6GHz, 5nm advanced process                                  |  |  |  |  |  |

|                            | SPECint2k17_Rate(64T) est: ~250 (3.0GHz)                                            |  |  |  |  |  |

|                            | L1: 64KB I-cache (parity), 64KB D-cache (ECC)                                       |  |  |  |  |  |

| Cache hierarchy            | Configurable up to 1MB L2 private cache (private, ECC)                              |  |  |  |  |  |

|                            | Configurable up to 64MB system-level cache (shared, ECC)                            |  |  |  |  |  |

| Memory/IO<br>Connectivity  | Provides standard AMBA CHI/AXI interfaces to support                                |  |  |  |  |  |

|                            | Up to 8x 40b DDR5 or LPDDR5 channel                                                 |  |  |  |  |  |

|                            | Up to 4x x16 PCIe/CXL Gen5 lanes                                                    |  |  |  |  |  |

|                            | Bifurcation support up to x4 for each x16 PCIe lanes                                |  |  |  |  |  |

| Die-to-Die<br>connectivity | Support for SMP compute or accelerator attach with UCIe or partner-specific D2D PHY |  |  |  |  |  |

| General I/O                | Expansion interface to connect slower speed peripheral like USB/<br>I3C/QSPI/etc.   |  |  |  |  |  |

| System<br>management       | System Control Processor(SCP)/                                                      |  |  |  |  |  |

|                            | Manageability Control processor(MCP)                                                |  |  |  |  |  |

| CSS area<br>(24/32/64c)    | ~53/61/198 mm sq                                                                    |  |  |  |  |  |

### armneoverse

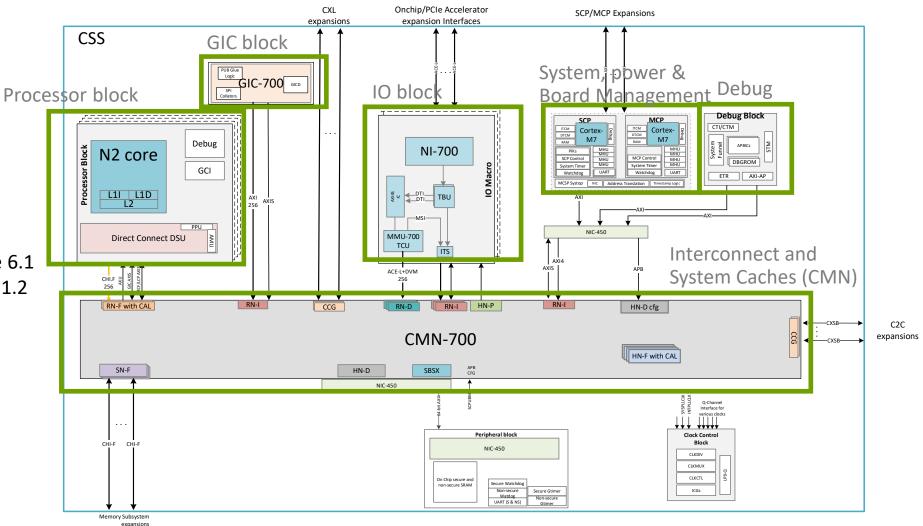

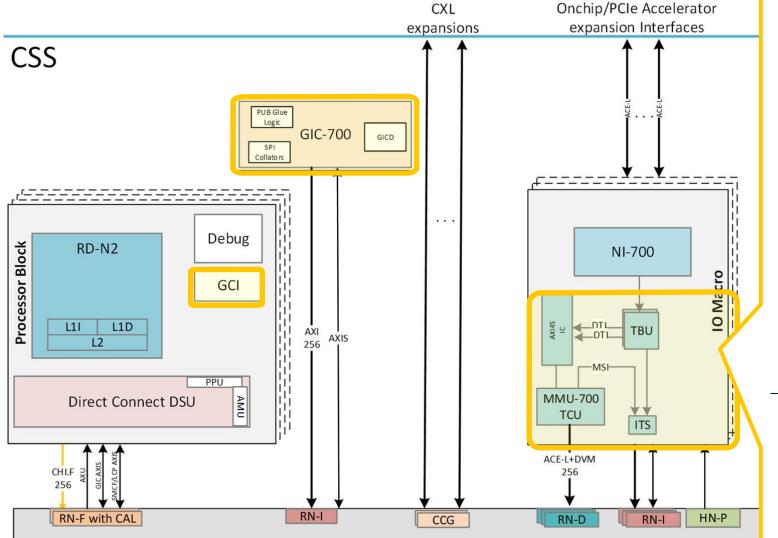

## Arm Neoverse CSS N2 Block Diagram

CSS is SystemReady **c**ompliant to: Arm Base System Architecture 1.0 Arm Server Base System Architecture 6.1 Arm Server Base Boot Requirements 1.2

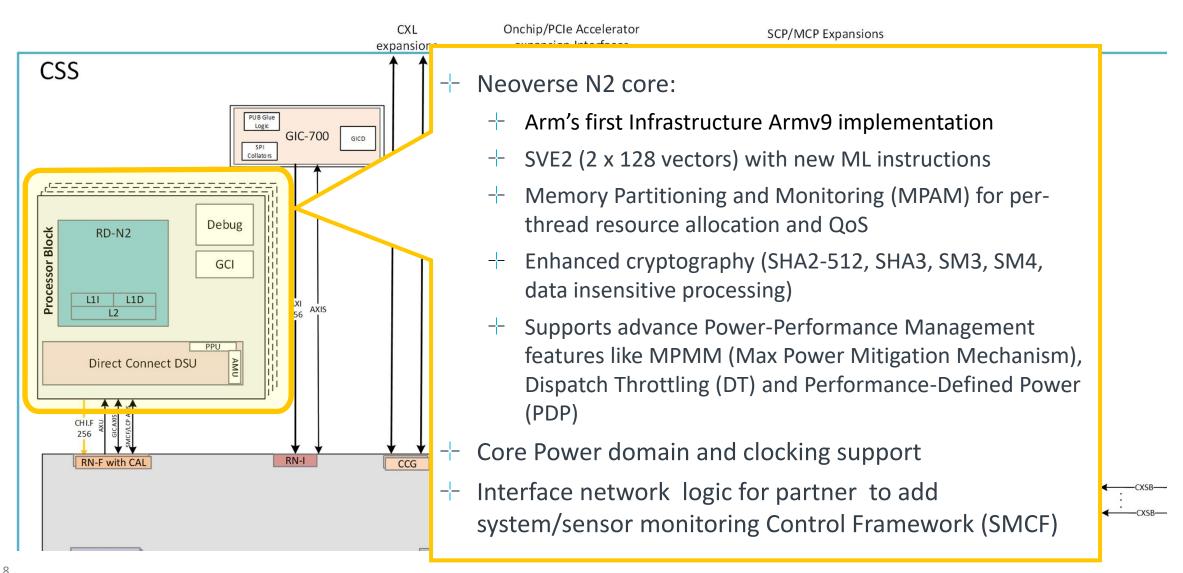

### **Processor Block**

### armneoverse

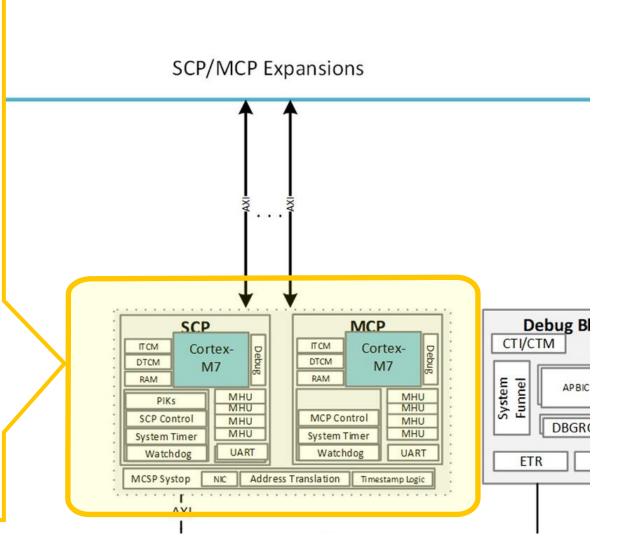

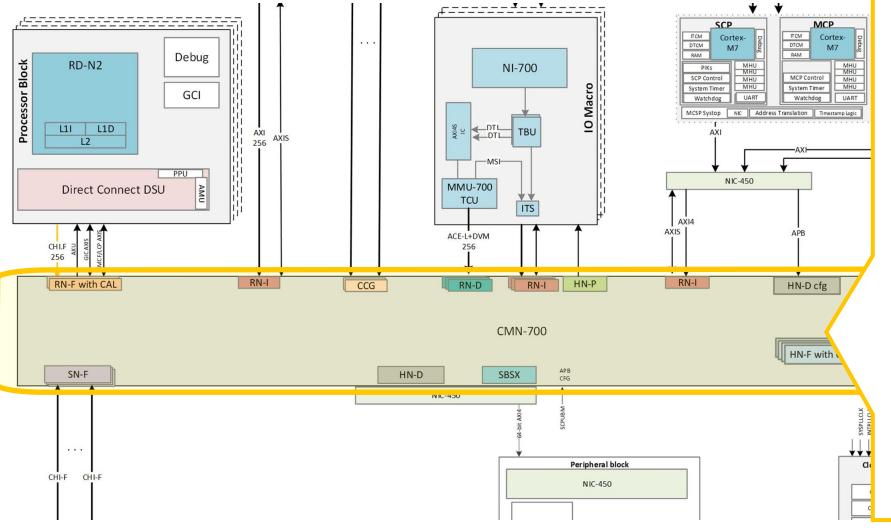

## System Control and Management

### -- System Control Processor (SCP):

- SCP is trusted core responsible for controlling system-related functions

- Controls resets, clock control, power and voltage domains

- + Responsible for all power management control

- Manageability Control Processor (MCP):

- MCP is a satellite controller communicating with the external Baseboard Management Controller (BMC) for the following functions:

- + On-chip management

- System reliability, accessibility, and serviceability (RAS) handling

- + Event logging and communication alerts

AVID

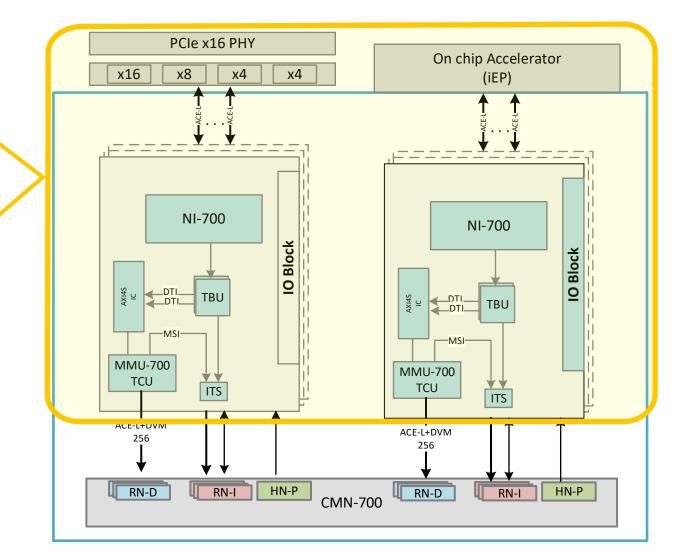

## System MMU and Interrupt Controller

- System MMU (MMU-700):

- Compliant with SMMU architecture version 3.2

- Provides address translation and virtualization support

- Armv9 & Armv8.4 support:

- MPAM, Secure-EL2 for multiple secure OS's and TLB range invalidate

- Single or two-stage address translation for PCIe and on-chip accelerators/devices

- GIC:

The GIC-700 (GICv4.1) is a generic interrupt controller that handles interrupts from peripherals to core and between cores

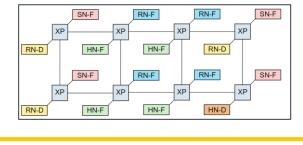

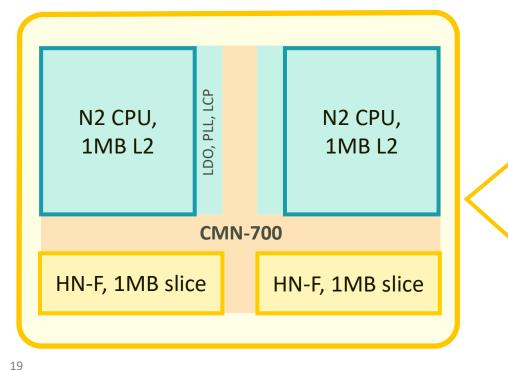

## System Interconnect

### -- Neoverse CMN-700:

- Mesh based coherent interconnect

- Shared system level

cache (SLC) for CPUs

and IO

- Latest Armv9.0-A and AMBA 5 features (Atomics, Stashing, and RAS)

- System Cache Groups for affinity and isolation

- + Fully coherent multichip support

### **Accelerator Attach**

CSS N2 provides an IO block with all the interrupt and address translation logic required for partners to add their specific on-chip accelerators or PCIe controllers for external devices

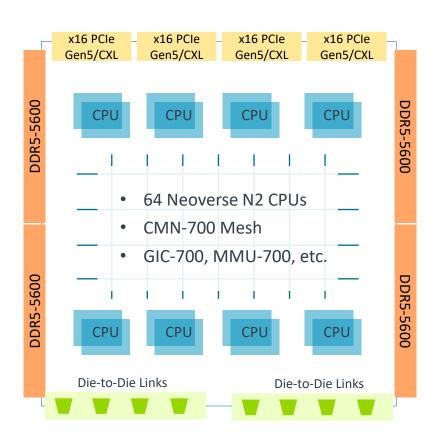

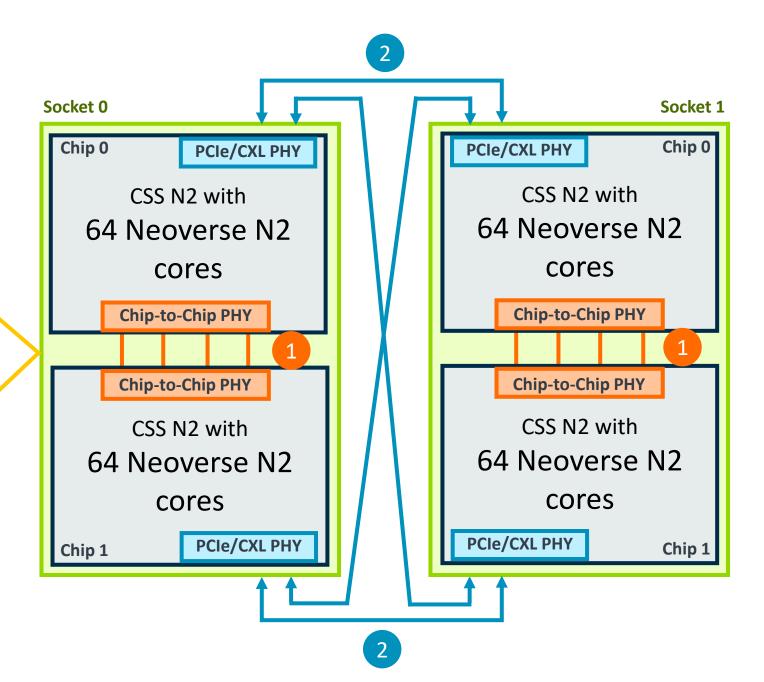

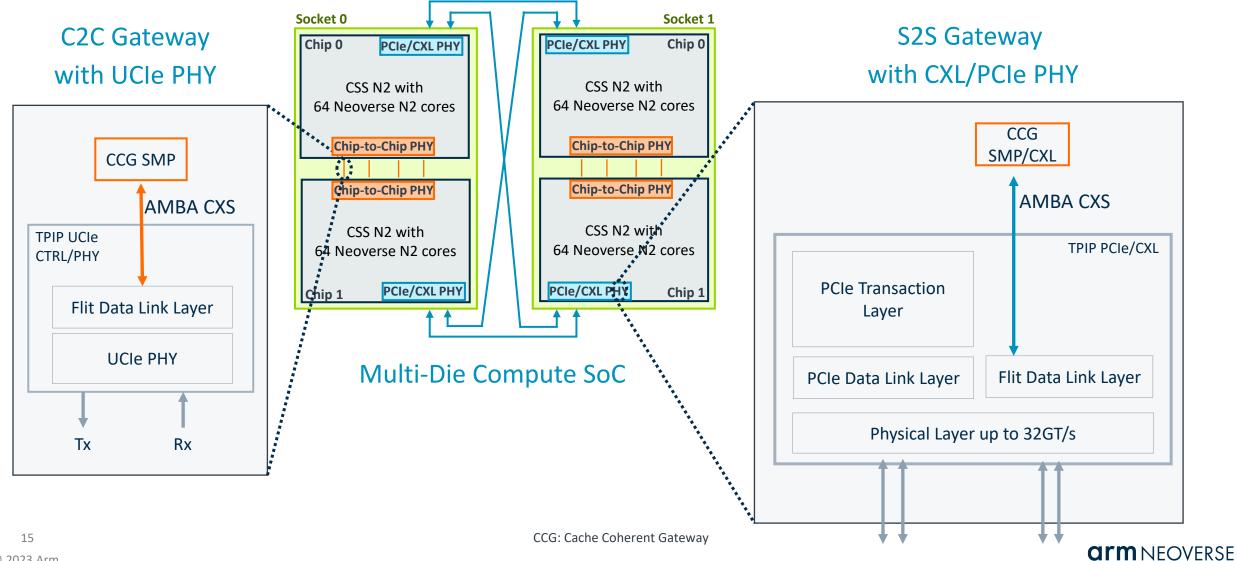

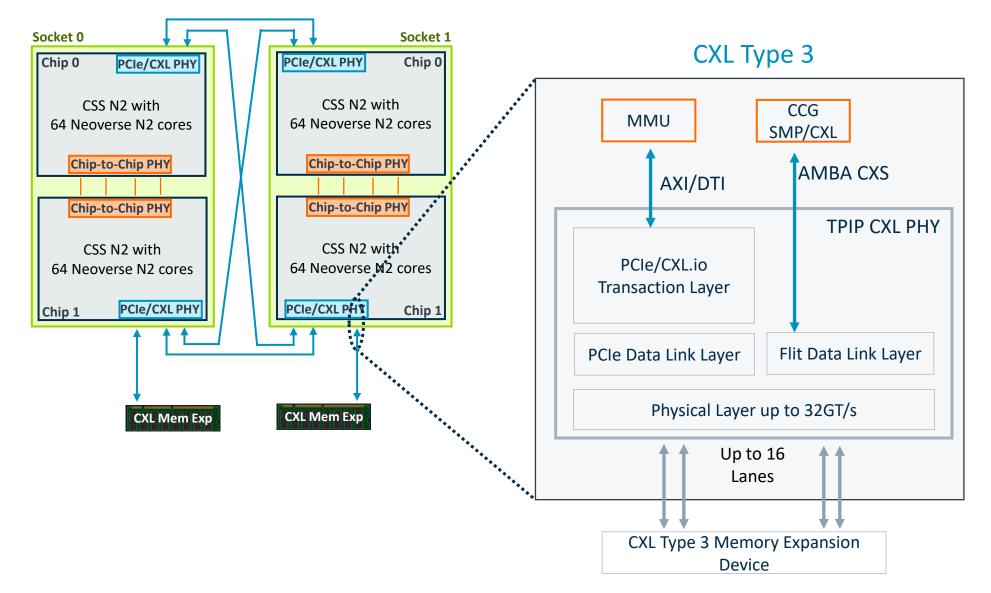

## **Core Scaling**

- + CSS N2 allows for connecting

- -- 2 chiplets per socket

- -- 2 sockets per system

- Scale up to 256 Neoverse N2 cores, delivering more performance in a fully coherent fashion

- SMP protocol for both chip-to-chip

(C2C) and socket-to-socket (S2S)

communication

- C2C links, can be UCle or partner specific C2C PHY

- Standard CXL PHY for S2S

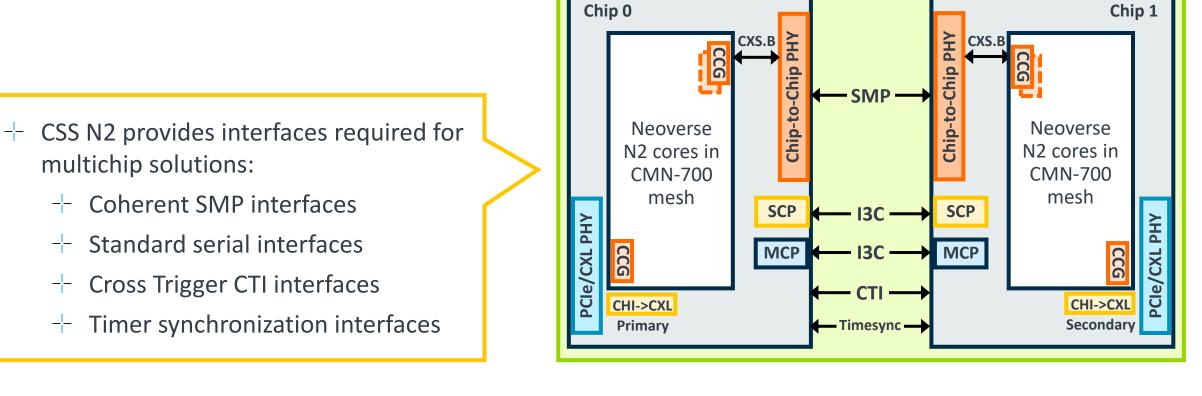

## **Multichip Interfaces**

### Socket 0

## **CMN** Gateway for SMP Connections

### armNeoverse

### CMN Gateway for CXL Type 3 Memory Expansion

### **arm** NEOVERSE

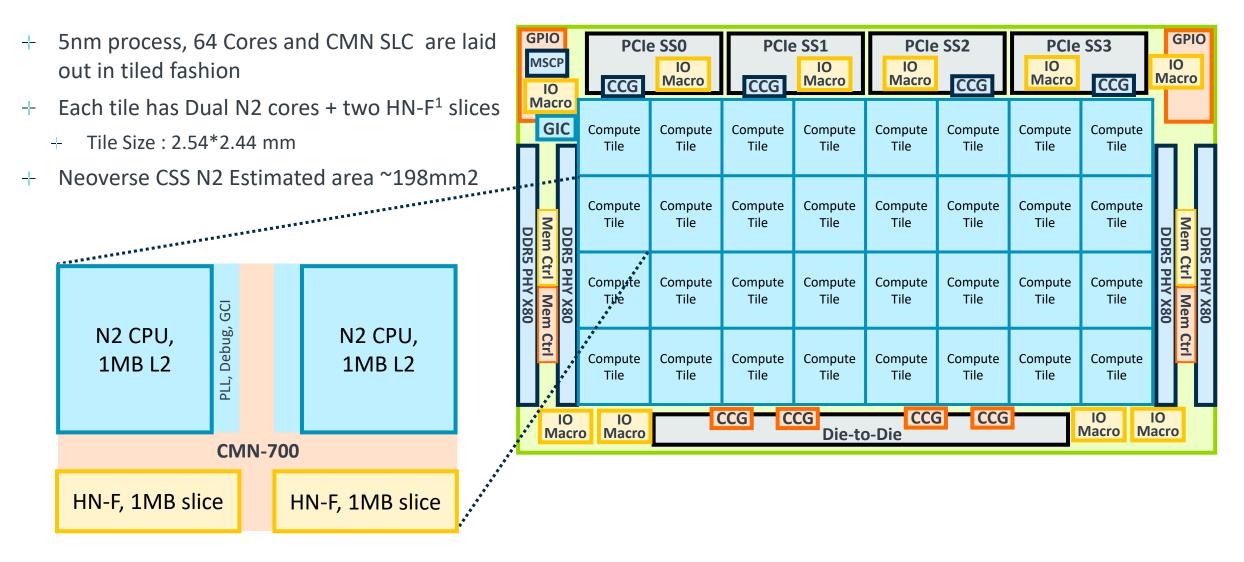

## Arm Neoverse CSS N2 Platform Floorplan Example

**arm** NEOVERSE

### Arm Neoverse CSS Platform Physical IP

- Arm builds physical IP including standard cell libraries, fast memory cache instances(FCIs) optimized for CSS

- N2 POP core implementation with optimized

PPA

- + Core and mesh configuration

- Metal stack

- + Floorplan

- -- EDA flow

- Sign-off

- N2 POP is delivered with reference flow scripts, physical IP, supporting utilities and documentation

- CMN-700 and HN-F FCI packages optimized for configuration and PPA

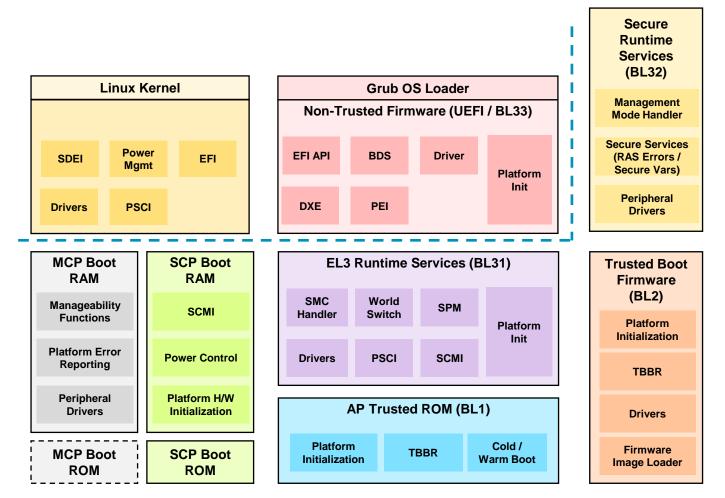

## **Neoverse Reference Design Platform Software**

Integrated reference stack targeting a Fixed Virtual platform (FVP) model of the system

- Designed to provide an extensible reference, bootstrapping partner engineering development. RTL for FPGA build.

- + Reference stack to demonstrate:

- Platform firmware ports for subsystem topology

- Integrating multiple components (firmware, OS, services)

- Software features

(boot flows, security, power management, etc.)

- Arm Neoverse Platform Software documentation

- + <u>https://neoverse-reference-</u> <u>design.docs.arm.com/en/latest/index.htm</u>

## The Future of Infrastructure is Built on Arm

- Neoverse CSS improves time-to-market and reduces development cost by delivering a pre-integrated, prevalidated, PPA-optimized compute subsystem to customers

- CSS N2 is the first generation of Neoverse CSS products, offering customization while leveraging over a decade of platform and software ecosystem standards development

| +          | + |  |  |  |  |                     |  |

|------------|---|--|--|--|--|---------------------|--|

| arr        |   |  |  |  |  | Thank You           |  |

|            |   |  |  |  |  | + Danke             |  |

|            |   |  |  |  |  | Gracias<br>+ Grazie |  |

|            |   |  |  |  |  | 谢谢                  |  |

|            |   |  |  |  |  | ありがとう               |  |

|            |   |  |  |  |  | Asante<br>+ Merci   |  |

|            |   |  |  |  |  | 감사합니다               |  |

|            |   |  |  |  |  | -धन्यवाद<br>-       |  |

|            |   |  |  |  |  | Kiitos<br>شکر ً ا   |  |

|            |   |  |  |  |  | ধন্যবাদ             |  |

| © 2023 Arm |   |  |  |  |  | תוְדה +             |  |

| +          | + |  |  |  |  |                     |  |

|------------|---|--|--|--|--|---------------------|--|

| arr        |   |  |  |  |  | Thank You           |  |

|            |   |  |  |  |  | + Danke             |  |

|            |   |  |  |  |  | Gracias<br>+ Grazie |  |

|            |   |  |  |  |  | 谢谢                  |  |

|            |   |  |  |  |  | ありがとう               |  |

|            |   |  |  |  |  | Asante<br>+ Merci   |  |

|            |   |  |  |  |  | 감사합니다               |  |

|            |   |  |  |  |  | -धन्यवाद<br>-       |  |

|            |   |  |  |  |  | Kiitos<br>شکر ً ا   |  |

|            |   |  |  |  |  | ধন্যবাদ             |  |

| © 2023 Arm |   |  |  |  |  | תוְדה +             |  |