## Notices and Disclaimers

Performance varies by use, configuration and other factors. Learn more at www.Intel.com/PerformanceIndex.

Performance results are based on testing as of dates shown in configurations and may not reflect all publicly available updates. See backup for configuration details. No product or component can be absolutely secure.

Intel contributes to the development of benchmarks by participating in, sponsoring, and/or contributing technical support to various benchmarking groups, including the BenchmarkXPRT Development Community administered by Principled Technologies.

Your costs and results may vary.

Intel technologies may require enabled hardware, software or service activation.

Some results may have been estimated or simulated.

Intel does not control or audit third-party data. You should consult other sources to evaluate accuracy.

All product plans and roadmaps are subject to change without notice.

Statements in this document that refer to future plans or expectations are forward-looking statements. These statements are based on current expectations and involve many risks and uncertainties that could cause actual results to differ materially from those expressed or implied in such statements. For more information on the factors that could cause actual results to differ materially, see our most recent earnings release and SEC filings at www.intc.com.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

Hot Chips 2023

#### Hot Chips 2023

# The Next Generation of High Performance, Energy-Efficient Computing: Intel® Xeon® Processors Built on Efficient-Core

Don Soltis Senior Principal Engineer, Xeon with Efficient-Core Architect, Intel

Stephen Robinson Intel Fellow, Efficiency Core Architect

## **Data Center Requirements Are Expanding**

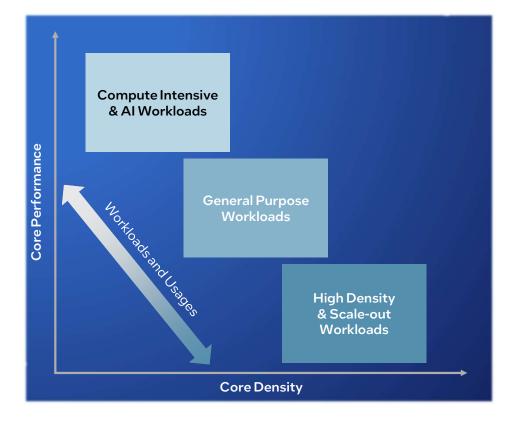

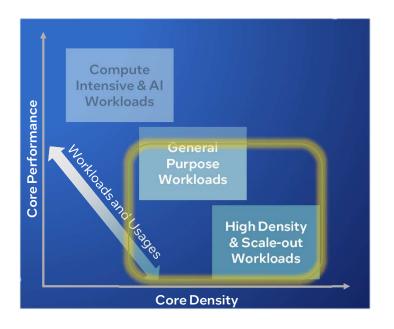

Continuing demand to increase core performance, power efficiency and throughput performance

Deliver the best performance per Watt at the desired core performance

Workload requirements place trade-offs between core performance & core density

Expanding deployment models demanding increased power, IO & memory bandwidth

Hot Chips 2023

intel. 3

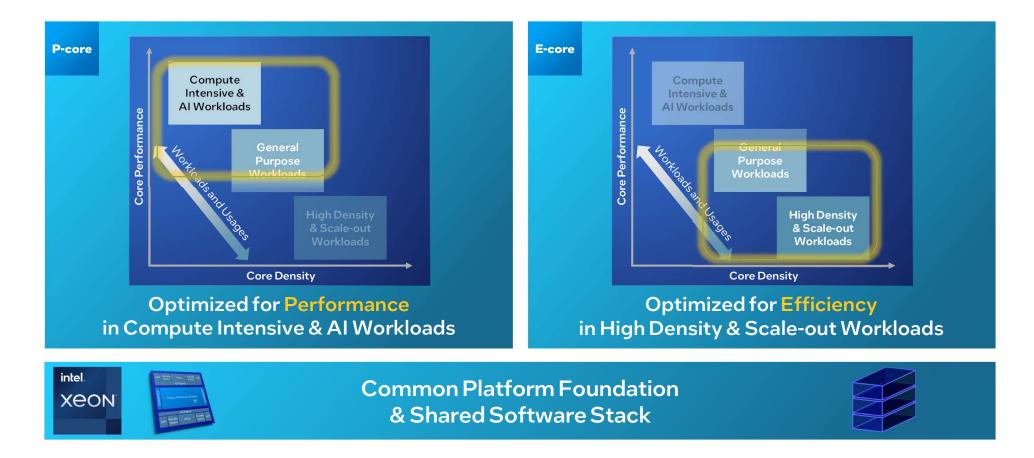

## **Expanded Xeon Product Portfolio with Optimized Processors**

Hot Chips 2023

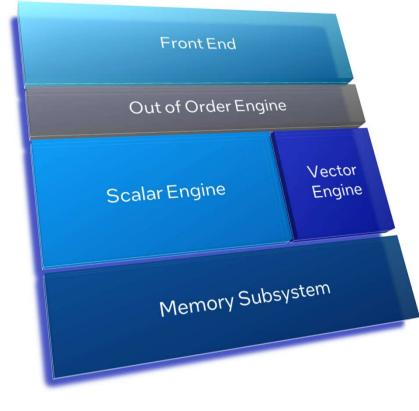

# Intel's Newest Data Center Efficiency Optimized E-Core Microarchitecture

Designed for scalable throughput performance

Optimized for power and density efficient throughput with:

Hot Chips 2023 Intel Xeon with E-cores (Sierra Forest)

intel. 5

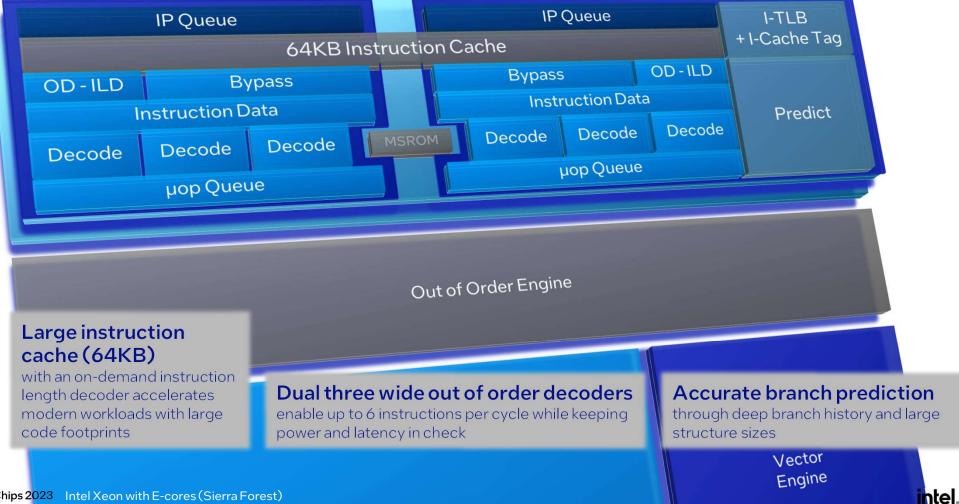

## **Core Instruction Control**

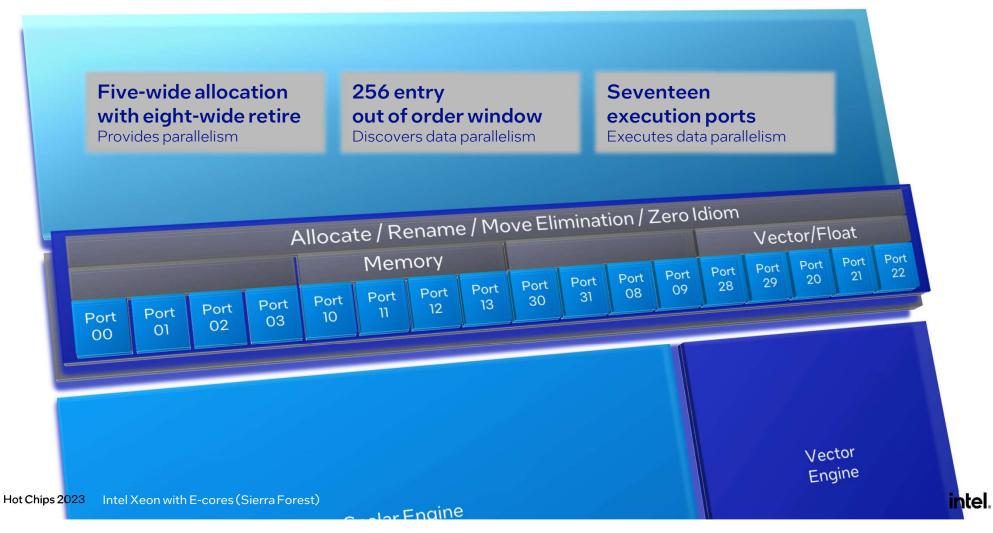

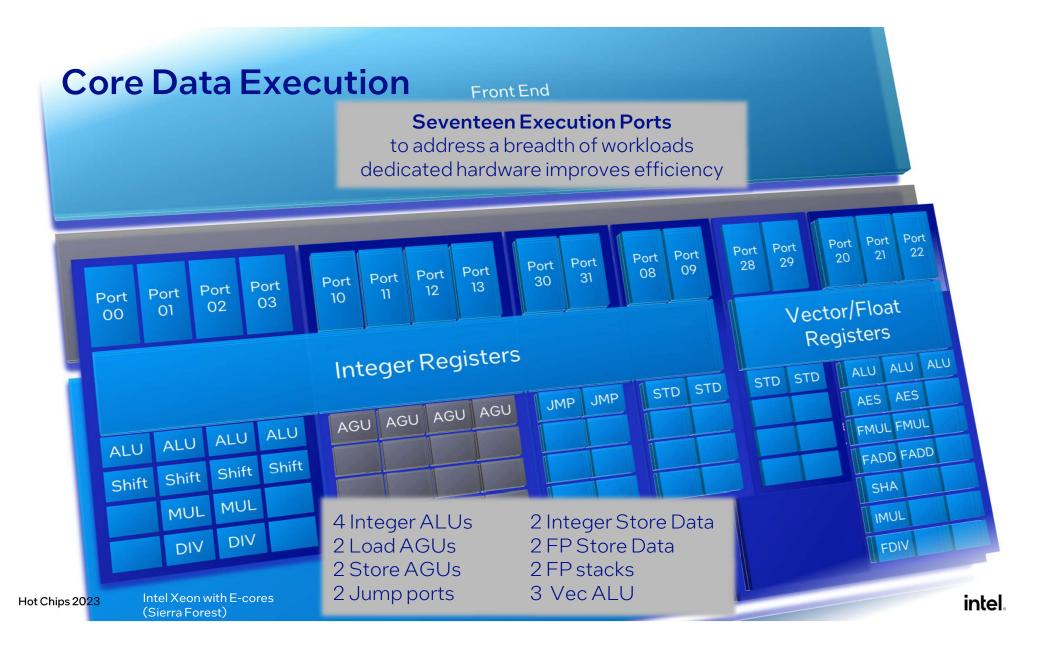

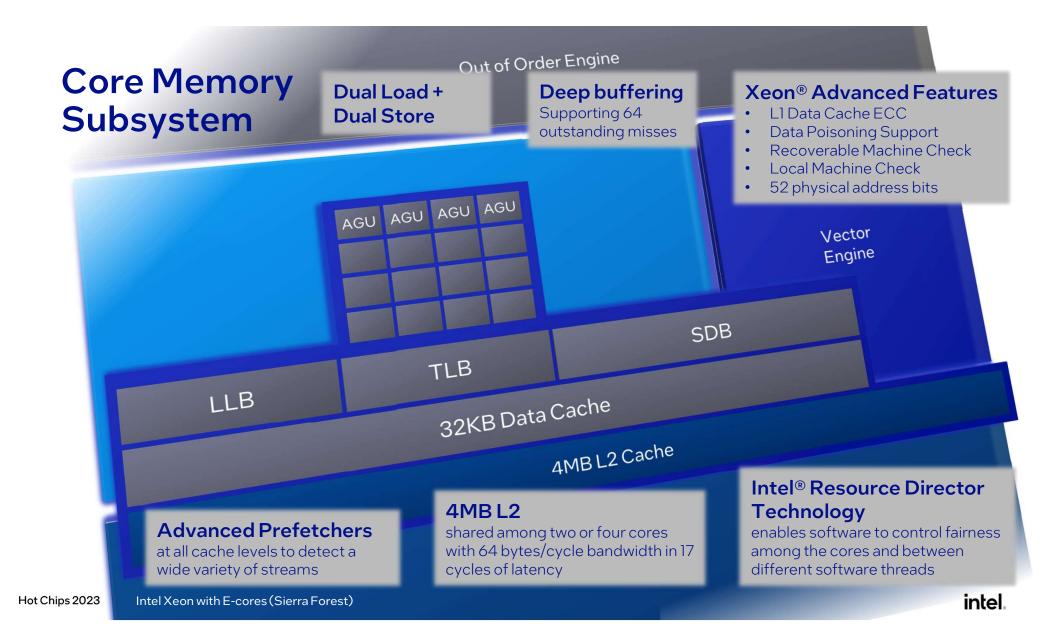

## **Core Execution**

7

| Modern<br>Instruction Set                                                                                                     | Vector                                                                         |                        |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------|

| Security Features                                                                                                             | Support for<br>Advanced Vector Instructions<br>with AI extensions              | ALU ALU ALU<br>AES AES |

| Intel <sup>®</sup> Control-Flow<br>Enforcement Technology<br>(Intel <sup>®</sup> CET) designed to improve<br>defense in depth | Wide Vector<br>Instruction Set Architecture                                    | FMUL FMUL<br>FADD FADD |

| <b>Intel® VT-rp</b><br>(Virtualization Technology<br>redirect protection) Supported                                           | Floating point multiply-<br>accumulate (FMA)<br>instructions for 2x throughput | SHA                    |

| Advanced speculative<br>execution validation<br>methodology                                                                   | Key instruction additions to<br>enable integer AI throughput                   | FDIV                   |

| Hot Chips 2023 Intel Xeon with E-cores (Sierra Forest) intel.                                                                 |                                                                                |                        |

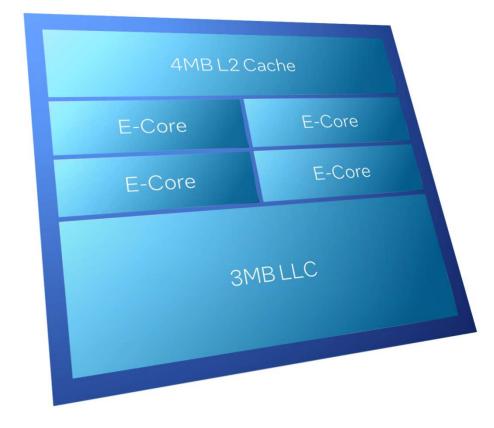

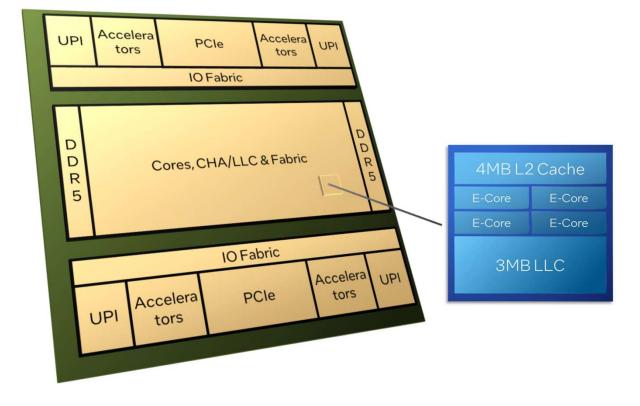

## **Core Tile**

#### **2 or 4 cores per module** Shared L2 cache Shared frequency and voltage domain Shared mesh fabric interface

#### **Each core is single threaded** Providing performance isolation

**LLC slice shared among all cores in socket** High bandwidth pipeline per slice

## **Package View**

## I/O Chiplet

Common with Xeon P-core (Granite Rapids) PCIe gen 5, CXL 2.0, UPI coherency links Crypto, compression, data streaming accelerators Self-boot

## **Compute Chiplet**

Mesh of core tiles Single domain, shared Last-Level cache DDR5 6400 interface

## Security Isolation<sup>1</sup>

Intel<sup>®</sup> Trusted Domain Extensions (Intel TDX) Intel<sup>®</sup> Software Guard Extensions (Intel SGX)

## Focus on Throughput Performance

Up to 288 cores (2S) 205W and higher power per socket

# Harness the Efficiency of Xeon with E-cores

Improve OpEx and CapEx Increased performance per Watt at increased core density

Augments Xeon breadth of coverage Same hardware, software and firmware

Vector and Al Instruction Support Including support for FP16, BF16 and INT8 data types

**Focus on throughput, density and efficiency** Optimize across full range of utilization

intel Xeon

Highly Scalable Architecture To Address the Throughput Efficiency Needs For the Next Decade of Compute

Hot Chips 2023

Intel Xeon with E-cores (Sierra Forest)

intel. 14

# Thank You

Hot Chips 2023

# References

TDX <u>https://www.intel.com/content/www/us/en/developer/articles/technical/intel-trust-domain-extensions.html</u>

VT-rp<u>https://www.intel.com/content/dam/www/central-libraries/us/en/documents/intel-virtualization-technologies-white-paper.pdf</u>

CET <u>https://www.intel.com/content/www/us/en/developer/articles/technical/technical-look-control-flow-enforcement-technology.html</u>

VNNI <u>https://community.intel.com/t5/Blogs/Tech-Innovation/Artificial-Intelligence-AI/Deep-Learning-Performance-Boost-by-Intel-VNNI/post/1335670</u>

CXL <a href="https://www.computeexpresslink.org/">https://www.computeexpresslink.org/</a>

## New instruction set extensions

https://www.intel.com/content/www/us/en/developer/articles/technical/intel-sdm.html#inpage-nav-4